| 系所名稱    | 類別       | 科目  | 節次  | 准考證號碼<br>(考生請填入) | 考試<br>日期 |

|---------|----------|-----|-----|------------------|----------|

| 電機工程研究所 | 碩 士 在職專班 | 電子學 | 第一節 |                  | 98/5/3   |

#### ※ 答案須寫在答案卷內,否則不予計分。

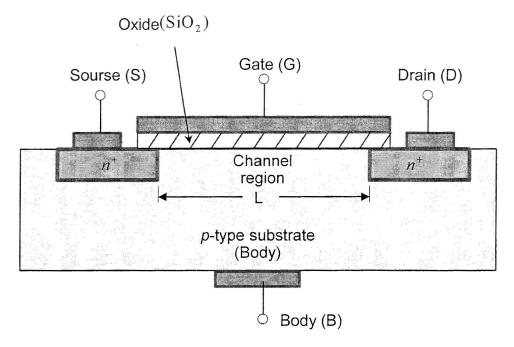

Fig. 1

- 1. The physical structure's cross section of the enhancement NMOS transistor is shown in Fig. 1, please choose the correct answer on each of the following questions. (10 %)

- (1) How to induce the n-channel on the p-type substrate? ( $V_t$  is the threshold voltage of the NMOS transistor.) (2%)

(a)

$$v_{DS} > 0$$

, (b)  $v_{DS} < 0$ , (c)  $v_{GS} > 0$ , (d)  $v_{GS} < 0$ , (e)  $v_{GS} > V_t$ , (f)  $v_{DS} > V_t$ , (g)  $v_{GS} < V_t$ , (h)  $v_{DS} < V_t$

(2) How to make the current flow through the channel induced? (2%)

(a)

$$v_{DS} > 0$$

, (b)  $v_{DS} < 0$ , (c)  $v_{GD} > 0$ , (d)  $v_{GD} < 0$

- (3) What is the current carried by? (a) free electrons, (b) free holes, (c) neutrons, (d) protons. (2%)

- (4) What is the current carriers flow direction? (a) from gate to source, (b) from drain to source, (c) from source to drain, (d) from drain to gate. (2%)

| 系所名稱    | 類別       | 科目  | 節次  | 准考證號碼<br>(考生請填入) | 考試日期   |

|---------|----------|-----|-----|------------------|--------|

| 電機工程研究所 | 碩 士 在職專班 | 電子學 | 第一節 |                  | 98/5/3 |

- (5) Which one is correct for the gate current  $i_G$ ? (a)  $i_G < 0$ , (b)  $i_G > 0$ , (c)  $i_G = 0$  (2%)

- 2. Please answer the following questions about the small-signal model of the NMOS transistor. (20%)

- (1) Please plot the low-frequency small-signal model of the NMOS transistor. (4%)

- (2) What is the input resistance? (4%)

- (3) What is the output resistance? (4%)

- (4) What is the small-signal gain? (4%)

- (5) What is the condition such that the small-signal model can be used for analysis of an NMOS amplifier? Please choose the correct answer as follows: (4%)

- (a)  $v_{gs} > 0$ , (b)  $v_{gs} << 0$ , (c)  $v_{gs} << 2(V_{gs} V_t)$ , (d)  $v_{gs} >> 2(V_{gs} V_t)$

- (e)  $V_{gs} >> (V_{gs} V_t)$

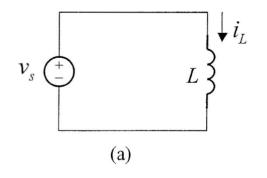

Fig. 2

- 3. (1) For the circuit in Fig.2(a), where  $v_s = \sin t$ ,  $L = 1 \, \text{H}$ . What is the value of  $i_L(t)$ ? (3%)

- (2) Please plot the waveforms of  $v_s(t)$  and  $i_L(t)$  in (1). What is the difference of phase angle between the  $v_s(t)$  and  $i_L(t)$ ? (3%)

| <b>系所名稱</b> | 類別       | 科目  | 節次  | 准考證號碼<br>(考生請填入) | 考試日期   |

|-------------|----------|-----|-----|------------------|--------|

| 電機工程研究所     | 碩 士 在職專班 | 電子學 | 第一節 |                  | 98/5/3 |

- (3) For the circuit in Fig.2(b), where  $v_s = \sin 10t$ ,  $L = 1 \,\mu\text{F}$ , What is the value of  $i_C(t)$ ?

- 4. Using an ideal operation amplifier and two resistors  $R_1$  and  $R_2$ , to design the following circuits:

- (a) an inverting amplifier with the gain of -10.(3%)

- (b) a non-inverting amplifier with the gain of 10. (3 %)

- (c) a voltage follower. (4 %)

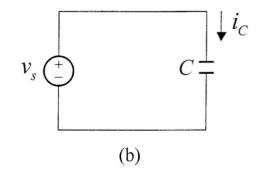

- 5. An integrator is shown in Fig. 3, in which the OP amplifier is ideal.  $R = 10 \text{ k}\Omega$ ,  $C = 1 \mu\text{F}$ . Please answer the following questions:

(a)

$$T(s) = \frac{V_o(s)}{V_i(s)}$$

. (4 %)

(b) Plot the Bode plot which includes the magnitude and phase. (6 %)

Fig. 3

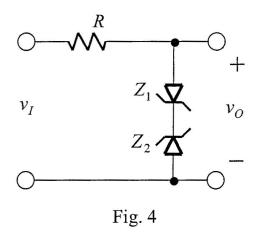

6. A limiter circuit is shown in Fig. 4, where the input signal is  $v_I(t) = 10\sin\omega t$ . The zener diode has  $V_{z1} = V_{Z2} = 6 \, \mathrm{V}$  and 0.7V voltage drop when conducting in forward direction.

| 系所名稱    | 類別       | 科目  | 節次  | 准考證號碼<br>(考生請填入) | 考試<br>日期 |

|---------|----------|-----|-----|------------------|----------|

| 電機工程研究所 | 碩 士 在職專班 | 電子學 | 第一節 |                  | 98/5/3   |

- (a) Please plot the input-output transfer characteristic curve of the circuit. (5 %)

- (b) Please plot the output voltage waveform (5 %)

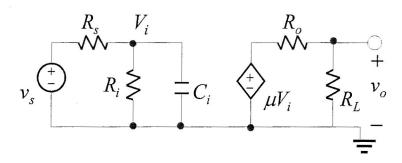

7. An amplifier is shown in Fig. 5, where

$R_s = 1 \text{ k}\Omega$ ,  $R_i = 100 \text{ k}\Omega$ ,  $C_i = 100 \text{ pF}$ ,  $\mu = 100 \text{ V/V}$ ,  $R_o = 100 \Omega$ ,  $R_L = 1 \text{ k}\Omega$ . Please answer the following questions:

(a)

$$T(s) = \frac{V_o(s)}{V_s(s)}$$

. (4 %)

- (b) What is the dc gain? (3 %)

- (c) What is the 3-dB frequency? (3 %)

Fig. 5

| 系所名稱    | 類別       | 科目  | 節次  | 准考證號碼<br>(考生請填入) | 考試日期   |

|---------|----------|-----|-----|------------------|--------|

| 電機工程研究所 | 碩 士 在職專班 | 電子學 | 第一節 |                  | 98/5/3 |

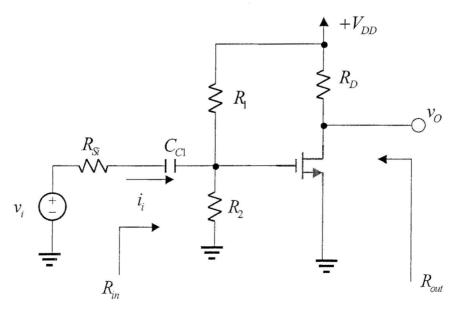

8. An NMOS Amplifier circuit is shown in Fig. 6.

$$V_t = 2.0 \text{ V}, K_n = \frac{1}{2} K_n \frac{W}{L} = 0.5 \text{ mA/V}^2, \lambda = 0.01 \text{ V}^{-1}$$

$$V_{DD} = 12 \text{ V}, R_1 = 90 \text{ K}\Omega, R_2 = 30 \text{ K}\Omega, R_D = 5 \text{ K}\Omega, R_{Si} = 4 \text{ K}\Omega.$$

$$I_{DQ} = K_n (V_{GSQ} - V_t)^2, \qquad g_m = 2K_n (V_{GSQ} - V_t), \quad r_o \approx \frac{1}{\lambda I_{DQ}} = \frac{V_A}{I_{DQ}}.$$

Please answer the following questions:

- (a) What is the amplifier configuration belong to? (Common source, common gate, or common drain) (2 %)

- (b) Find the dc or quiescent gate-to-source voltage,  $V_{\rm GSQ}$  , and the quiescent drain current,  $I_{\rm DQ}$  . (4 %)

- (c) Please plot the small-signal model of the circuit, with the resistance  $r_o$  included..(4%)

- (d) Find the voltage gain:  $A_v = v_o / v_i$  (4%)

- (e) Find the input resistance  $R_{in}$  . (3 %)

- (f) Find the output resistance  $R_{out}$  . (3 %)

第5頁,共5頁

Fig. 6